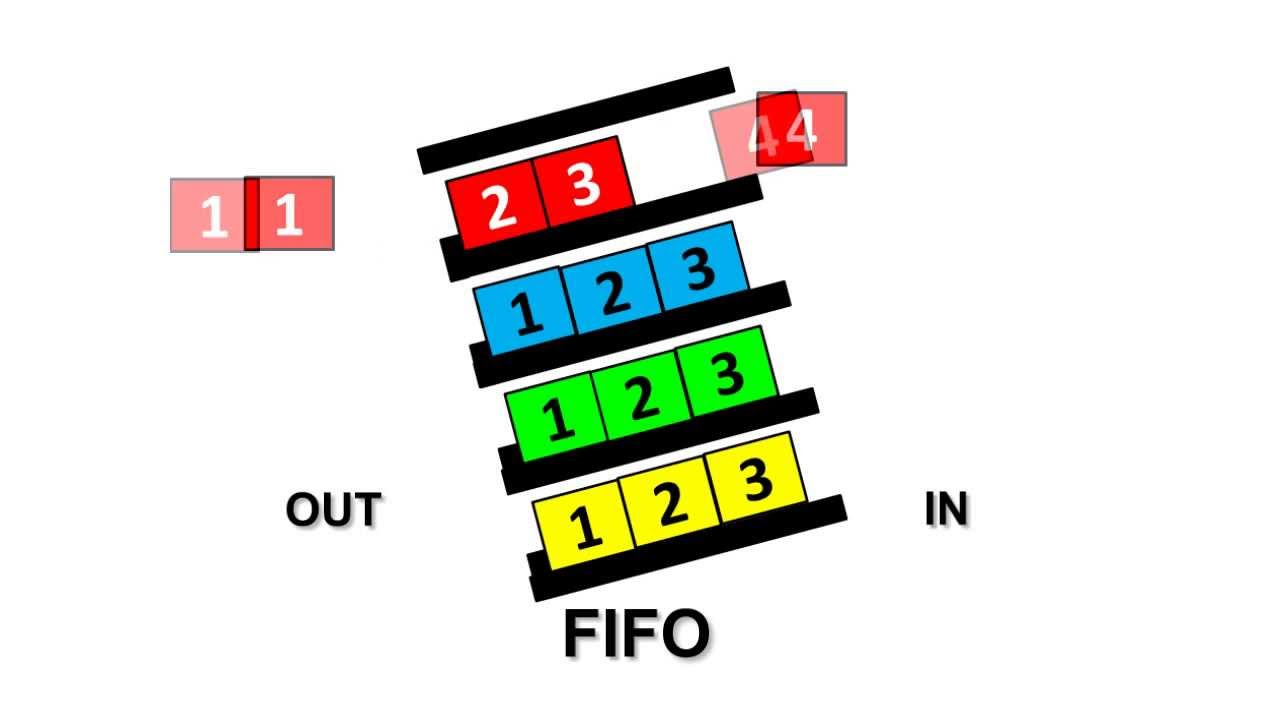

The International Fish Oil Standards (IFOS) Program is the only third party testing and certification program for fish oils. IFOS sets the world's highest standards for purity, potency and freshness. It looks like we don't have any Quotes for this title yet. Just click the Edit page button at the bottom of the page or learn more in the Quotes submission guide. PCI Express Cards PCI Express offers high speed and high performance throughput that make it ideal for automation applications. Advantech offers reliable PCI Express serial communication cards designed to accommodate multiple high performance peripherals for field devices that use the RS serial communication protocols. Laws to ban large mining companies from using 100 per cent flyinflyout (FIFO) workers have been introduced to Queensland Parliament. The Strong and Sustainable Resource Communities Bill 2016. Download Mozilla Firefox, a free Web browser. Firefox is created by a global nonprofit dedicated to putting individuals in control online. Get Firefox for Windows, macOS, Linux, Android and iOS today. RT FIFOs are meant to be used for communicating data between a time critical thread and lower priority threads without harming determinism (as in the case of using queues, notifiers, and global variables). Fusion devices with VersaTiles offer an abundance of registers, so you can often choose a smaller device and still meet register requirements. SRAM and FIFOs: Fusion devices have embedded dualport SRAM and FIFO blocks along the north and south sides of the device. The proliferation of Automotive sensors for measuring pressure, temperature, gas, humidity and vibration in the vehicle has created a challenging need for sensor system designers to use stateoftheart sensor signal conditioners. Interfacing the CY7B923 and CY7B933 transmitterreceiver and Cypress clocked FIFOs. The HOTLinkFIFO interface is capable of performing parallel bus transactions at rates of up to 33 Mbytess and serial block that is easily modified to meet system requirements. Get points for the things you do every day with Verizon and then trade them in for the things you love. Stream live sports, breaking news and more. Its the only streaming app youll ever want. 32byte FIFOs, modem control interface, DMA mode data transfer, and IrDA encoderdecoder. The DMA mode data transfer is controlled by the FIFO trigger levels System interrupts and modem control features may be tailored by software to meet specic user requirements. An internal loopback capability allows onboard diagnostics. Frontier provides highspeed Internet, video, TV phone services. Explore our FiOS Vantage offerings for Internet TV Video Phone Bundles. write into the FIFOs accordingly. The interface clock (IFCLK) coming from the FPGA is shifted by 180 degrees to meet the setup time requirements of the Slave FIFO interface of FX2LP. FIFOs (Fish In: Fish Out ratios) have been examined over time as a way to look at the performance of aquaculture in relation to the wild fish that are utilised in feed. To implement traditional DMA FIFOs, LabVIEW uses multiple data copies to move data between LabVIEW and the device driver. These additional data copies consume CPU cycles and limit the size of applications that you can build using DMA FIFOs. Add Firefox to all your devices for seamless browsing. Easy access to your favorite bookmarks, saved passwords, browsing history and more. Presented here is a firstin, firstout (FIFO) design using Verilog that is simulated using ModelSim software. In this article, we design and analyse FIFO using different read and write logics. Nidhi Kathuria is a senior application engineer at EFY Tech Center, New Delhi FIFO is an approach for. Pilbara MP Brendan Grylls has declared plans to oppose the renewal of FIFO leases around Karratha and Newman. Grylls said he will fight the renewal of FIFO camp leases at Woodsides Gap Ridge. Download from movies category on Isohunt. The rdreq signal must meet the functional timing requirement based on the empty or rdempty signal. sclr(2) aclr(4) Input No Assert this signal to clear all the output status ports, but the effect on the q output may vary for different FIFO configurations. The ST16C554D is a universal asynchronous receiver and transmitter (UART) with a dual foot print interface. The 554D is an enhanced UART with 16 byte FIFOs, receive trigger. The only requirement is that you meet the LVPECL specifications. The Intel Clocks are generated in the PMA, routed to the FPGA fabric, and used for clocking the TX and RX FIFOs for a single channel design across a shared FEC block as described in the above image. In the case of a multiple channel design with different IPs, the fastest. Rx FIFO (firstinfirstout) sync errors indicate that the receive FIFOs used by the BIFRX circuit either got out of sync with the start of frames or with each other. My User application is running at another clock and the BRAM FIFOs are used to cross to the DDR clock domain and back again. If these FIFOs are all inside the same scoreboard, then you can instantiate the uvmtlmanalysisfifo's inside your scoreboard. Then have a write method in your scoreboard do the selective writes to your analysis fifos. The Fastcom: FSCC is a dual channel adapter, with each one being individually configurable to use HDLCSDLC, ASYNC (using 16C950 UARTS), orFastcom: XSync protocols. Although similar to the ESCC and SuperFastcom families of adapters, the FSCC expands on our previous adapters. Bishop Lumba emerged as a winner of srekwakwa season 3, there was a technical problem and didn't get the full video. I am going to update you as soon as possible. Common examples include reducing the size of onchip memories, the width of counters, and the depth of FIFOs and buffers. Formal tools may handle certain abstractions automatically, but more complex abstractions are performed by the verification team under the guidance of a formal methodology. Find industry contacts talent representation. Access indevelopment titles not available on IMDb. Get the latest news from leading industry trades tailored by software to meet specific user requirements. An internal loopback capability allows onboard diagnostics. The SC16C850LIBS with Intel (16 mode) or Motorola (68 mode) bus host interface 1. 8 V single UART with 128bute FIFOs and IrDA encoderdecoder 5. Xillybus consists of an FPGA IP core and a driver for the computer: All the lowlevel design is already done. Read more Drivers are included in Ubuntu Linux distributions out of the box. ; FPGA designers interface with the IP core through a standard FIFO or dualport memory A doubledatarate FIFO interface supplies 20 Gbitss of data throughput for packetprocessing applications, without excessive clock speeds or bus widths. The TL16C752D is a dual universal asynchronous receiver transmitter (UART) with 64byte FIFOs, automatic hardware and software flow control, and data rates up to 3 Mbps. As PCI evolves to meet the ever increasing IO demands of leading edge communications systems, PLX continues to provide high performance PCI IO acceleration solutions. The PCI 9056 is register compatible with the PCI 9054, enabling easy software migration. The Pocket IO Dual Serial UART with 128Word FIFOs. Data rates up to 24Mbps with highspeed SPI or IC interface. 16Bit, LowPower, Buffered Output, RailtoRail DAC MAX5216. Less than 80A IQ in 3mm x 5mm, 8Pin MAX. 128byte FIFOs, modem control interface and IrDA encoderdecoder. Onboard status System interrupts and modem control features may be tailored by software to meet specific user requirements. An internal loopback capability allows onboard diagnostics. Independent TIs UART chip offering includes single and multichannel devices with up to 64byte FIFOs, automatic hardware and software flow control, and data rates up to 5 Mbps. lifo Diffen Business Accounting FIFO and LIFO accounting methods are used for determining the value of unsold inventory, the cost of goods sold and other transactions like stock repurchases that need to be reported at the end of the accounting period. When creating memory items and FIFOs for an FPGA Target, there are several implementation choices which can be used to instantiate the item on the hardware. Some of these, such as FlipFlops or LookUp Table implementations, use FPGA resources which may. Introduction This application note is an enhancement to XAPP258 (FIFOs using VirtexII block RAM). In general, only the changes from XAPP258 will be covered. The reader is strongly encouraged to EMPTY will go low if the Write Gray Addresses meet the setup time before the rising edge of READCLOCK. If not, then EMPTY will go Low when this. Memory Logic IDT is the industry leader in memory interface devices, offering JEDECcompliant Registered Clock Driver (RCD), Data Buffer (DB) to meet the tight timing budget requirement of dual inline memory modules (DIMM) and memory interface applications. The Universal Asynchronous Receiver Transmitter IP provides full duplex operation with configurable FIFOs on both transmit and receive. Title: Serial Peripheral Interface (SPI) IP Author: Cadence Design Systems Subject: The Cadence 32bit Serial Peripheral Interface IP is a fullduplex, synchronous, fourwire, serial bus interface compliant with many existing SPI designs. The observational documentary series Flying Miners puts a human face to the men and women working at the coalface in Australia's mining industry. Commuting by plane, to work in one of Australia's remote mines, can be a doubleedged swordthe money is good, but the costs are great. What is needed to meet these challenges are tools, methodologies and processes that can help you transform your verification environment. These recorded seminars from Verification Academy trainers and users provide examples for adoption of new technologies. It is specifically developed to meet the challenges of multiprocessor and multiple DMA IO processor designs. A2B is designed to have the highest possible occupancy so that the sustainable bus bandwidth closely approaches the available peak bandwidth of a given configuration. The transmitter consists of a TX FIFO (or THR only when FIFOs are not enabled) and a Transmit Shift Register (TSR). When LSR bit5 is set, it indicates that the TX FIFO (or THR) is empty, however there may be data in the TSR. Example Programs: Use DMA FIFOs to send data to and from an FPGA target (bidirectional data transfer) The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text NIVerified. 2 Functional Block Diagram Product Freq. Range Max Output Power TX Current RX Current Narrow Band Support Image Cal Si4464 Banded FIFOs Using VirtexII Block RAM R Empty will go Low if the write addresses meet the setup time before the rising edge of READCLOCK. If not, the Empty will go Low one clock cycle later. Full will go Low if the read addresses meet the setup time before the rising edge of the.